- NEWS AND VIEWS

- 05 March 2026

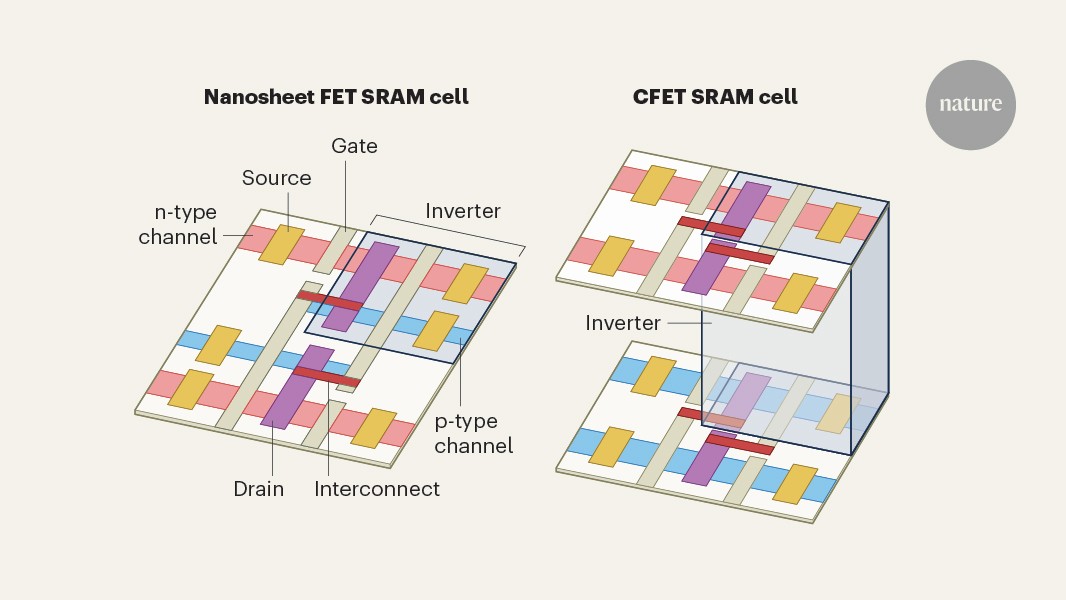

Logical circuits have been built from nanosheet stacks of various transistors, which could make electronic devices faster and more compact.

By

-

Xiong Xiong

-

Xiong Xiong is in the School of Integrated Circuits and the Beijing Advanced Innovation Center for Integrated Circuits, Peking University, Beijing, China.

-

-

Yanqing Wu

-

Yanqing Wu is in the School of Integrated Circuits and the Beijing Advanced Innovation Center for Integrated Circuits, Peking University, Beijing, China.

-

In urban areas where land is scarce, skyscrapers and high-rise buildings enable homes and businesses to be densely packed into small areas. Now, in a paper presented at the 2025 IEEE International Electron Devices Meeting, Liao et al.1 of Taiwan Semiconductor Manufacturing Company (TSMC) apply this principle to integrated circuits — reporting two logical circuits in which two kinds of transistor are stacked on top of each other. In the decades since transistors were invented, the electronics industry has continuously packed them more densely onto chips, but the physical limitations of conventional transistor materials make it challenging to continue this trajectory. Liao and colleagues’ work shows that, with innovations in materials and device design, it is still possible to develop ways to optimize chip space.

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$32.99 / 30 days

cancel any time

Subscribe to this journal

Receive 51 print issues and online access

$199.00 per year

only $3.90 per issue

Rent or buy this article

Prices vary by article type

from$1.95

to$39.95

Prices may be subject to local taxes which are calculated during checkout

Additional access options:

doi: https://doi.org/10.1038/d41586-026-00249-w

References

Liao, S. et al. In Proc. 2025 IEEE Int. Electron Devices Meet. https://doi.org/10.1109/IEDM50572.2025.11353820 (IEEE, 2025).

Liao, S. et al. In Proc. 2024 IEEE Int. Electron Devices Meet. https://doi.org/10.1109/IEDM50854.2024.10873334 (IEEE, 2024).

Park, J. et al. In Proc. 2023 IEEE Int. Electron Devices Meet. https://doi.org/10.1109/IEDM45741.2023.10413694 (IEEE, 2023).

Ryckaert, J. et al. In Proc. 2018 IEEE Symp. VLSI Technol. 141–142 (IEEE, 2018).

Radosavljević, M. et al. In Proc. 2023 IEEE Int. Electron Devices Meet. https://doi.org/10.1109/IEDM45741.2023.10413678 (IEEE, 2023).

Ha, D. et al. In Proc. 2025 Symp. VLSI Technol. Circuits https://doi.org/10.23919/VLSITechnologyandCir65189.2025.11074874 (IEEE, 2025).

Cavalcante, C. et al. In Proc. 2025 Symp. VLSI Technol. Circuits https://doi.org/10.23919/VLSITechnologyandCir65189.2025.11075156 (IEEE, 2025).

Reboh, S. et al. In Proc. 2025 Symp. VLSI Technol. Circuits https://doi.org/10.23919/VLSITechnologyandCir65189.2025.11074866 (IEEE, 2025).

Competing Interests

The authors declare no competing interests.

Electrostatic-based transfer keeps 2D materials ultra-clean

Electrostatic-based transfer keeps 2D materials ultra-clean

Computer processors built from 2D materials

Computer processors built from 2D materials